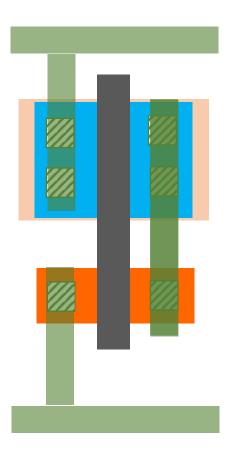

///Oxide///////

N+ Source

P-type Body

N+ Drain

# **Integrated Circuit Layout Basic**

Hanwool Jeong

hwjeong@kw.ac.kr

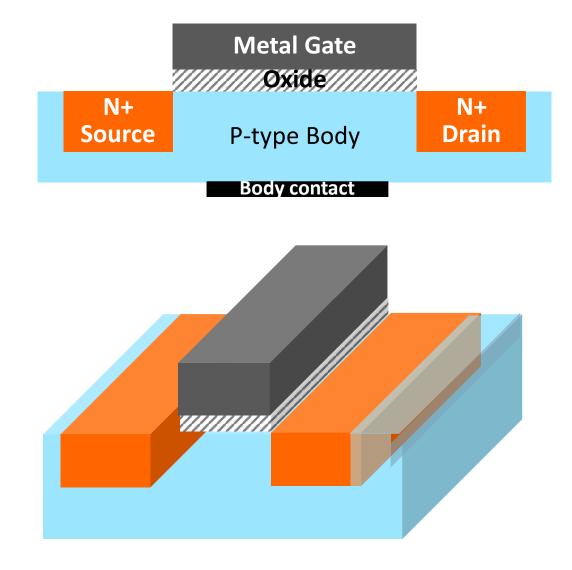

### **Revisit NMOSFET Structure**

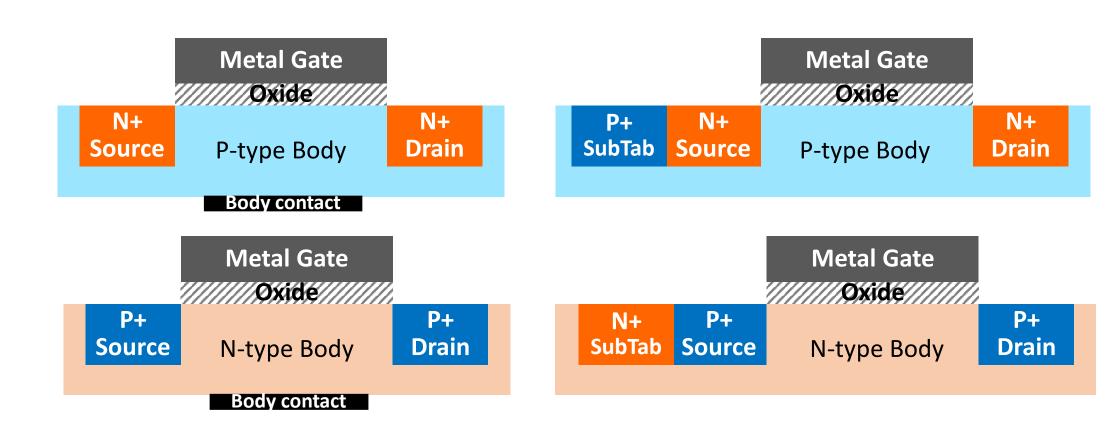

#### **NMOSFET & PMOSFET**

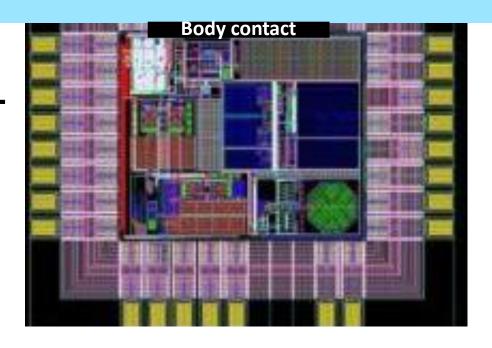

Body bias is performed through substrate tab.

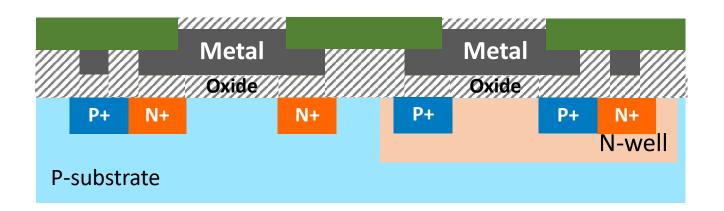

#### **How Would Process Look Like?**

- How can nMOSFET and pMOSFET get together? → N-well

- How can distant be connected? → Metal layer interconnect

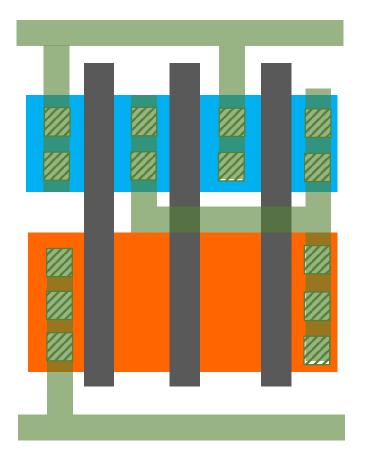

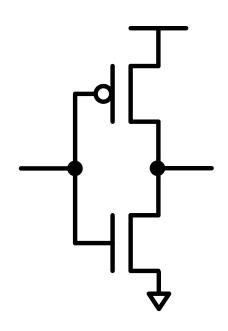

#### **How Would Inverter Look Like?**

- We will see the top view.

- Assume that body tab is omitted.

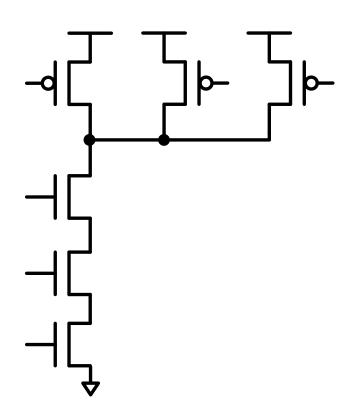

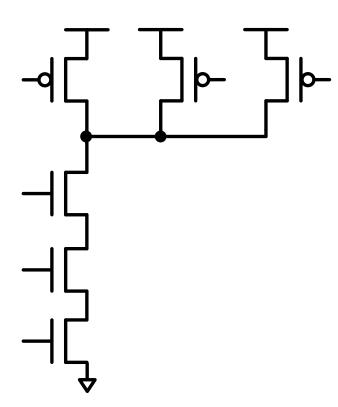

## Naïve Drawing 3-input NAND Layout

• If you consider each transistor separately, the resultant layout will be very inefficient.

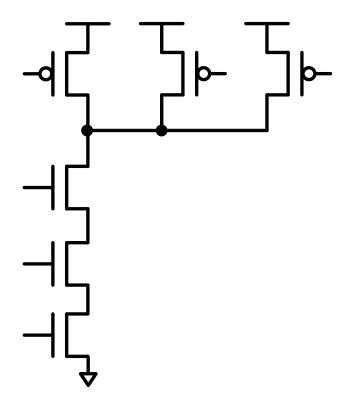

## **3-input NAND Layout**

- See how diffusions can be shared.

- Compare the parasitic cap in pulldown and pull-up networks